Digilent Arty Handleiding

Overzicht

Arty is een kant-en-klaar ontwikkelplatform dat is ontworpen rond de Artix-7 Field Programmable Gate Array (FPGA) van Xilinx. Het is speciaal ontworpen voor gebruik als een MicroBlaze Soft Processing System. Wanneer Arty in deze context wordt gebruikt, wordt het het meest flexibele verwerkingsplatform dat u zich kunt wensen voor uw collectie, in staat om zich aan te passen aan wat uw project ook vereist. In tegenstelling tot andere Single Board Computers is Arty niet gebonden aan een enkele set verwerkingsrandapparatuur: het ene moment is het een krachtpatser vol met UARTS, SPI's, IIC's en een Ethernet MAC, en het volgende moment is het een nauwgezette tijdwaarnemer met een dozijn 32-bits timers.

- Xilinx Artix-35T FPGA (xc7a35ticsg324-1L)

- 33.280 logische cellen in 5200 slices (elke slice bevat vier 6-input LUT's en 8 flip-flops);

- 1.800 Kbits aan snel blok RAM;

- Vijf klokbeheertegels, elk met een phase-locked loop (PLL);

- 90 DSP-slices;

- Interne kloksnelheden van meer dan 450 MHz;

- On-chip analoog-digitaal converter (XADC).

- Programmeerbaar via JTAG en Quad-SPI Flash

- Systeemfuncties

- 256 MB DDR3L met een 16-bits bus @ 667 MHz

- 16 MB Quad-SPI Flash

- USB-JTAG-programmeercircuits

- Gevoed via USB of een 7V-15V-bron

- Systeemconnectiviteit

- 10/100 Mbps Ethernet

- USB-UART-brug

- Interactie- en sensorische apparaten

- 4 schakelaars

- 4 knoppen

- 1 resetknop

- 4 LED's

- 4 RGB-LED's

- Uitbreidingsconnectoren

- 4 Pmod-connectoren

- Arduino/chipKIT Shield-connector

Arty is volledig compatibel met de krachtige Vivado ® Design Suite. Het wordt ondersteund onder de gratis WebPACK™-licentie, zodat ontwerpen zonder extra kosten kunnen worden geïmplementeerd. Deze gratis licentie omvat de mogelijkheid om MicroBlaze™ soft-core processorontwerpen te maken. Ontwerpresources, voorbeeldprojecten en tutorials kunnen worden gedownload in het Arty Resource Center, toegankelijk via reference.digilentinc.com.

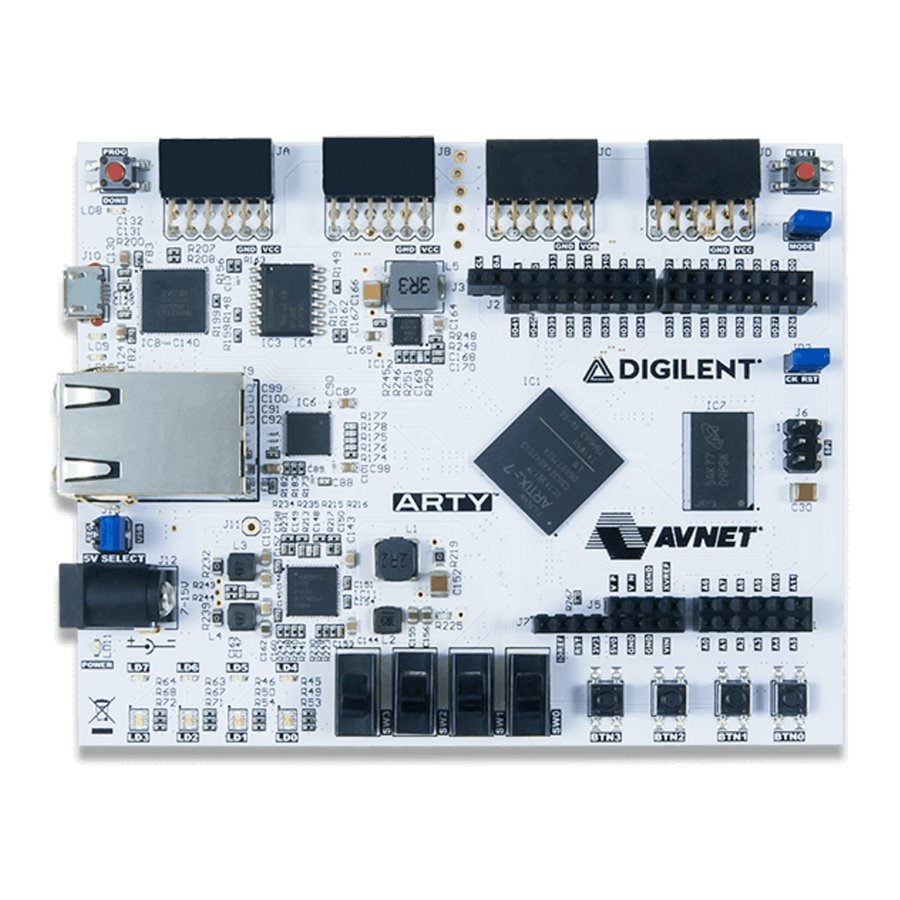

| Callout | Beschrijving |

| 1 | FPGA-programmering DONE LED |

| 2 | Gedeelde USB JTAG/UART-poort |

| 3 | Ethernet-connector |

| 4 | Stroomselectie-jumper (Ext. voeding/USB) |

| 5 | Stroomaansluiting (voor optionele ext. voeding) |

| 6 | Stroom goed LED |

| 7 | Gebruikers-LED's |

| 8 | Gebruikersschuifschakelaars |

| 9 | Gebruikersdrukknopen |

| 10 | Arduino/chipKIT-shieldconnectoren |

| 11 | SPI-header (Arduino/chipKIT-compatibel) |

| 12 | chipKIT-processorresetjumper |

| 13 | FPGA-programmeringsmodus (JTAG/Flash) |

| 14 | chipKIT-processorreset |

| 15 | Pmod-headers |

| 16 | FPGA-programmeringsresetknop |

| 17 | SPI Flash |

| 18 | Artix FPGA |

| 19 | Micron DDR3-geheugen |

| 20 | Analoge apparaten ADP 5052-voeding |

Tabel 1. Arty hardware callout-beschrijvingen.

Ontwerpen met Arty

Wat Arty zo flexibel maakt, is zijn FPGA. Naast hun vele functies hebben FPGA's de mogelijkheid om te transformeren in een aangepaste software-gedefinieerde System-on-a-Chip (SoC). Deze "Soft SoC" FPGA-configuraties worden grafisch ontworpen met behulp van een tool genaamd Vivado IP Integrator (Vivado IPI). In deze tool worden vooraf gebouwde randapparatuurblokken vanuit een uitgebreide bibliotheek gesleept en in uw verwerkingssysteem geplaatst zoals u dat wilt. Deze vooraf gebouwde randapparatuur omvat timers, UART/SPI/IIC-controllers en veel van de andere apparaten die u doorgaans in een SoC of zou aantreffen

microcontroller. Ambitieuze gebruikers zullen ook ontdekken dat ze hun eigen randapparatuurblokken kunnen maken door ze te schrijven in een Hardware Definition Language (HDL), specifiek Verilog of VHDL. Voor degenen die geen interesse hebben in het leren van HDL, kan de Xilinx High Level Synthesis-tool worden gebruikt om aangepaste randapparatuurblokken te definiëren door ze in C te schrijven.

De Soft SoC-configuraties van Arty worden aangedreven door MicroBlaze-processorkernen. MicroBlaze is een 32-bits RISC soft processor core, speciaal ontworpen voor gebruik in Xilinx FPGA's. De MicroBlaze-processor in een Arty SoC-configuratie draait doorgaans op 100 MHz, hoewel het mogelijk is om uw SoC zo te ontwerpen dat hij op meer dan 200 MHz kan werken. Arty ondersteunt grote MicroBlaze-programma's met veeleisende geheugenvereisten door 16 MB niet-vluchtig programmageheugen en 256 MB DDR3L RAM te bieden.

Nadat u uw soft SoC-configuratie voor Arty hebt ontworpen, kunt u beginnen met het schrijven van programma's ervoor. Dit wordt gedaan door uw SoC-ontwerp uit Vivado IPI te exporteren naar de Xilinx Software Development Kit (XSDK), een Integrated Development Environment (IDE) voor het ontwerpen/debuggen van MicroBlaze-programma's in C. Na de IPI-naar-XSDK-overdracht wordt XSDK automatisch geconfigureerd om bibliotheken en voorbeelden op te nemen voor de randapparatuurblokken die u in uw SoC hebt opgenomen. Op dit punt lijkt het programmeren van de Arty erg op het programmeren van andere SoC- of microcontrollerplatforms: programma's worden in C geschreven, via USB naar het board geprogrammeerd en vervolgens optioneel in hardware gedebugd. Soft SoC-configuraties en MicroBlaze-programma's kunnen ook in het 16 MB niet-vluchtige programmageheugen worden geladen, zodat ze direct na het inschakelen van Arty worden uitgevoerd.

Hoewel de Arty bijzonder geschikt is voor MicroBlaze Soft SoC-ontwerpen, kan hij ook worden geprogrammeerd met een Register-Transfer Level (RTL)-circuitbeschrijving, net als elk ander FPGA-ontwikkelplatform. Deze ontwerpworkflow vereist dat u uw RTL-circuit beschrijft met behulp van een HDL in Vivado, en maakt geen gebruik van de Vivado IPI- of XSDK-tools. Ontwerpen op deze manier heeft veel voordelen, maar is heel anders dan het programmeren van een single board computer, en wordt in plaats daarvan gebruikt door degenen die bekend zijn met FPGA-ontwerp of geïnteresseerd zijn in het ontwerpen en implementeren van een digitaal circuit dat geen processor bevat.

Voedingen

Het Arty-board heeft een 5V-voeding nodig om te werken. Deze voeding kan afkomstig zijn van de Digilent USB-JTAG-poort (J10) of kan worden afgeleid van een 7 tot 15 Volt DC-voeding die is aangesloten op Power Jack (J12) of Pin 8 van Header J7. Header J13, die zich tussen de stroomaansluiting en de Ethernet-connector bevindt, wordt gebruikt om te bepalen welke bron wordt gebruikt.

Een power-good LED (LD11), aangestuurd door de "power good" (PWRGD)-uitgang van de ADP5052-regelaar, geeft aan dat het board stroom ontvangt en dat de onboard voedingen naar verwachting functioneren. Een overzicht van het Arty-stroomcircuit wordt hieronder weergegeven.

De USB-poort kan voldoende stroom leveren voor de overgrote meerderheid van de ontwerpen. Een paar veeleisende toepassingen, waaronder alle toepassingen die meerdere randapparatuurboards aansturen, vereisen mogelijk meer stroom dan de USB-poort kan leveren. Sommige toepassingen moeten mogelijk ook werken zonder te zijn aangesloten op de USB-poort van een pc. In deze gevallen kan een externe voeding of een batterijpakket worden gebruikt.

Een externe voeding kan worden gebruikt door deze aan te sluiten op Power Jack J12 en een jumper in de "REG"-positie op Header J13 te plaatsen. De voeding moet een coaxiale, midden-positieve plug met een interne diameter van 2,1 mm (of 2,5 mm) gebruiken en een spanning van 7 tot 15 Volt DC leveren. De voeding moet een minimumstroom van 1 ampère leveren. Idealiter moet de voeding 36 Watt vermogen kunnen leveren (12 Volt DC, 3 ampère).

Een extern batterijpakket kan worden gebruikt door de positieve pool van de batterij aan te sluiten op pin 8 van J7 (gelabeld VIN) en de negatieve pool op pin 7 van J7 (gelabeld GND), zoals weergegeven in de onderstaande afbeelding. Om het batterijpakket als stroombron van het board te gebruiken, moet een jumper in de "REG"-positie op Header J13 worden geplaatst. De batterij moet een spanning tussen 7 en 15 volt DC leveren en mag NIET worden geplaatst terwijl er een voeding is aangesloten op Power Jack J12.

Spanningsregelaarcircuits van Analog Devices en Texas Instruments creëren de vereiste 3,3V-, 1,8V-, 1,35V-, 1,25V- en 0,95V-voedingen van de 5V-voeding. In het geval dat een externe voeding of batterijpakket wordt gebruikt, levert de onboard Analog Devices 5V-regelaar de 5V-bron. De onderstaande tabel geeft aanvullende informatie (typische stromen zijn sterk afhankelijk van de FPGA-configuratie en de verstrekte waarden zijn typisch voor ontwerpen van gemiddelde grootte/snelheid).

| Voeding | Circuits | Apparaat | Stroom (max/typisch) |

| 5V | On-board regelaars, RGB-LED's | IC12: Analog Devices ADP2384 | 3,5A/0,375A tot 2A |

| 3,3V | FPGA I/O, klokken, flash, Pmods, LED's, knoppen, schakelaars, USB-poort, Ethernet | IC11: Analog Devices ADP5052 | 2,2A/NA |

| 0,95V | FPGA Core en Block RAM | IC11: Analog Devices ADP5052 | 1,0A/0,2A tot 0,8A |

| 1,8V | FPGA Auxiliary | IC11: Analog Devices ADP5052 | 1,0A/NA |

| 1,35V | DDR3L en bijbehorende FPGA-bank | IC11: Analog Devices ADP5052 IC13: Texas Instruments | 1,0A/NA |

| 1,25V | XADC analoge referentie | IC13: Texas Instruments REF3012 | 25mA/NA |

Tabel 2. Informatie over spanningsregelaarcircuits.

Spanningsbewaking van externe voeding

Het Arty-board bevat circuits voor het bewaken van de spanning van een externe voeding die is aangesloten op Power Jack J12, of een extern batterijpakket dat is aangesloten op header J7. Een spanningsdeler wordt gebruikt om de ongereguleerde ingangsspanning, VU, te schalen zodat deze binnen het bereik (0-1V) valt dat de on-chip 12-bits ADC kan meten. De ongereguleerde ingangsspanning, VU, wordt gedeeld door 16 en vervolgens ingevoerd in Auxiliary Channel 2 op de XADC van de Artix 35T. Toepassingen die de spanning van een externe voeding willen bewaken, kunnen Channel 2 van de XADC configureren als een unipolaire ingang en een conversie uitvoeren om een digitale waarde te ontvangen die overeenkomt met de ingangsspanning. De onderstaande afbeelding geeft een overzicht waarmee een externe voedingsspanning kan worden bewaakt.

Stroombewaking van FPGA Core-voeding

Het Arty-board bevat circuits voor het bewaken van de stroom die wordt verbruikt door de FPGA-core. De stroom wordt bewaakt door de spanning te meten over een 10 milliohm meetweerstand die is geplaatst tussen de uitgang van de 0,95V schakelende regelaar (IC11, Channel 2) en het VCC0V95-netwerk. Een stroommeetversterker (IC15, Texas

Instrument's INA199A1) die is aangesloten over de meetweerstand, biedt een versterking van 50 en produceert een uitgangsspanning van 500 millivolt per ampère stroom. De uitgang van de stroommeetversterker wordt ingevoerd in Auxiliary Channel 10 op de XADC van de Artix 35T. Toepassingen die het stroomverbruik van de FPGA Core en Block RAM willen bewaken, kunnen Channel 10 van de XADC configureren als een unipolaire ingang en een conversie uitvoeren om een digitale waarde te ontvangen die overeenkomt met de versterkte meetweerstandspanning. De onderstaande afbeelding geeft een overzicht van de circuits waarmee de FPGA Core Supply-stroom kan worden bewaakt.

Vermogensbewaking van 5V-voeding

Het Arty-board bevat circuits voor het bewaken van de spanning van de 5 Volt-voeding en de stroom die door deze voeding wordt verbruikt. Een spanningsdeler wordt gebruikt om de 5V-ingangsspanning te schalen zodat deze binnen het bereik (0-1V) valt dat de onchip 12-bits ADC kan meten. De 5V-voedingsspanning wordt gedeeld door 5,99 en vervolgens ingevoerd in auxiliary Channel 1 op de XADC van de Artix 35T. Een combinatie van een 5 milliohm stroommeetweerstand en een stroommeetversterker (IC14, Texas Instruments INA199A1) wordt gebruikt om een uitgangsspanning van 250 millivolt per ampère stroom te produceren. De uitgang van de stroommeetversterker wordt ingevoerd in Auxiliary channel 9 op de XADC van de Artix 35T. Toepassingen die het momentane stroomverbruik van het Arty-board willen bewaken, kunnen Channels 1 en 9 van de XADC configureren als unipolaire ingangen en vervolgens een gelijktijdige conversie van de twee kanalen uitvoeren om digitale waarden te ontvangen die kunnen worden gebruikt om het momentane stroomverbruik te berekenen. De onderstaande afbeelding geeft een overzicht van de circuits waarmee het 5V Supply-stroomverbruik kan worden bewaakt.

FPGA-configuratie

Na het inschakelen moet de Artix-7 FPGA worden geconfigureerd (of geprogrammeerd) voordat deze een functie kan uitvoeren. U kunt de FPGA op een van de volgende twee manieren configureren:

- Een pc kan de Digilent USB-JTAG-circuits (poort J10) gebruiken om de FPGA te programmeren wanneer de stroom is ingeschakeld.

- Een bestand dat is opgeslagen in het niet-vluchtige seriële (SPI) flashapparaat, kan via de SPI-poort naar de FPGA worden overgebracht.

![Digilent - Arty - FPGA-configuratie FPGA-configuratie]()

Afbeelding 3 toont de verschillende opties die beschikbaar zijn voor het configureren van de FPGA. Een on-board "mode"-jumper (JP1) selecteert of de FPGA wordt geprogrammeerd door de Quad-SPI-flash bij het opstarten.

De FPGA-configuratiegegevens worden opgeslagen in bestanden die bitstreams worden genoemd en de extensie .bit hebben. De ISE- of Vivado-software van Xilinx kan bitstreams maken van VHDL-, Verilog- of schemagebaseerde bronbestanden (in de ISE-toolset wordt EDK gebruikt voor MicroBlaze-ontwerpen op basis van embedded processoren).

Bitstreams worden opgeslagen in vluchtige geheugencellen in de FPGA. Deze gegevens definiëren de logische functies en circuitverbindingen van de FPGA en blijven geldig totdat ze worden gewist door de stroom van de kaart te verwijderen, op de resetknop te drukken die is aangesloten op de PROG-ingang, of door een nieuw configuratiebestand te schrijven met behulp van de JTAG-poort.

Een Artix-7 35T-bitstream is doorgaans 17.536.096 bits. De tijd die nodig is om de Arty te programmeren, kan worden verkort door de bitstream te comprimeren voordat deze wordt geprogrammeerd en vervolgens de FPGA de bitstream zelf te laten decomprimeren tijdens de configuratie. Afhankelijk van de ontwerpcomplexiteit kunnen compressieverhoudingen van 10x worden bereikt. Bitstreamcompressie kan worden ingeschakeld in de Xilinx-tools (ISE of Vivado) om plaats te vinden tijdens het genereren. Raadpleeg de Xilinx-documentatie voor de toolset die wordt gebruikt voor instructies over hoe u dit moet doen.

Nadat de FPGA succesvol is geprogrammeerd, zorgt deze ervoor dat de "DONE"-LED oplicht. Als u op enig moment op de knop "PROG" drukt, wordt het configuratiegeheugen in de FPGA gereset. Na het resetten zal de FPGA onmiddellijk proberen zichzelf opnieuw te programmeren met de methode die is geselecteerd door de programmeermode-jumpers.

De volgende paragrafen geven meer details over het programmeren van de Arty met behulp van de verschillende beschikbare methoden.

JTAG-configuratie

De Xilinx-tools communiceren doorgaans met FPGA's met behulp van de Test Access Port en Boundary-Scan Architecture, ook wel JTAG genoemd. Tijdens de JTAG-programmering wordt een .bit-bestand overgebracht van de pc naar de FPGA met behulp van de ingebouwde Digilent USB-JTAG-circuits (poort J10) of een externe JTAG-programmer, zoals de Digilent JTAG-HS2, die is aangesloten op poort J8. U kunt de JTAG-programmering op elk moment uitvoeren nadat de Arty is ingeschakeld, ongeacht of de mode-jumper (JP1) is ingesteld. Als de FPGA al is geconfigureerd, wordt de bestaande configuratie overschreven met de bitstream die via JTAG wordt verzonden. Het niet instellen van de mode-jumper (zoals te zien in afbeelding 3) is handig om te voorkomen dat de FPGA wordt geconfigureerd vanuit Quad-SPI Flash totdat er een JTAG-programmering plaatsvindt.

Het programmeren van de Arty met een niet-gecomprimeerde bitstream met behulp van de ingebouwde USB-JTAG-circuits duurt meestal ongeveer 6 seconden. JTAG-programmering kan worden gedaan met behulp van de hardwaremanager in Vivado of de iMPACT-tool die bij ISE is inbegrepen.

Quad-SPI-configuratie

Omdat het geheugen van de FPGA op de Arty vluchtig is, is het afhankelijk van het Quad-SPI-flashgeheugen om de configuratie tussen stroomcycli op te slaan. Deze configuratiemodus wordt Master SPI genoemd. De blanco FPGA neemt de rol van master op zich en leest het configuratiebestand uit het flashapparaat bij het inschakelen. Daartoe moet eerst een configuratiebestand naar de flash worden gedownload. Bij het programmeren van een niet-vluchtig flashapparaat wordt een bitstream-bestand in een proces in twee stappen naar de flash overgebracht. Eerst wordt de FPGA geprogrammeerd met een circuit dat flashapparaten kan programmeren en vervolgens worden gegevens via het FPGA-circuit naar het flashapparaat overgebracht (deze complexiteit is voor de gebruiker verborgen door de Xilinx-tools). Dit wordt indirecte programmering genoemd. Nadat het flashapparaat is geprogrammeerd, kan het de FPGA automatisch configureren bij een volgende inschakel- of resetgebeurtenis, zoals bepaald door de instelling van de mode-jumper (zie afbeelding 3). Programmeerbestanden die zijn opgeslagen in het flashapparaat, blijven behouden totdat ze worden overschreven, ongeacht stroomcyclusgebeurtenissen.

Het programmeren van de flash kan wel vier tot vijf minuten duren, wat vooral te wijten is aan het lange wisproces dat inherent is aan de geheugentechnologie. Eenmaal geschreven, kan de FPGA-configuratie echter erg snel zijn — minder dan een seconde. Bitstreamcompressie, SPI-busbreedte en configuratiesnelheid zijn factoren die worden beheerd door de Xilinx-tools die de configuratiesnelheid kunnen beïnvloeden. De Arty ondersteunt x1-, x2- en x4-busbreedtes en datasnelheden tot 50 MHz voor Quad-SPI-programmering.

Quad-SPI-programmering kan worden gedaan met behulp van de hardwaremanager in Vivado of met de iMPACT-tool die bij ISE is inbegrepen.

Geheugen

De Arty-kaart bevat twee externe geheugens: een 256 MB DDR3L SDRAM en een 128 Mb (16 MB) niet-vluchtig serieel flashapparaat. De DDR3L-module is via de industriestandaardinterface verbonden met de FPGA. De seriële flash bevindt zich op een speciale quad-mode (x4) SPI-bus. De verbinding en een pintoewijzing tussen de FPGA en externe geheugens worden hieronder weergegeven.

DDR3L

De Arty bevat een MT41K128M16JT-125-geheugencomponent, waardoor een enkele rank-, 16-bits brede interface ontstaat. Deze is gerouteerd naar een HR (High Range) FPGA-bank met een vermogen van 1,35 V met een geregelde single-ended trace-impedantie van 50 ohm. Interne afsluitingen van 50 ohm in de FPGA worden gebruikt om de tracekenmerken aan te passen. Op dezelfde manier worden aan de geheugenzijde on-die terminations (ODT) gebruikt voor impedantieaanpassing.

Voor een goede werking van het geheugen moet een geheugencontroller en een fysieke laaginterface (PHY) in het FPGA-ontwerp worden opgenomen. De eenvoudigste manier om dit op de Arty te bereiken, is door de Xilinx 7-series memory interface solutions core te gebruiken die is gegenereerd door de MIG (Memory Interface Generator) Wizard. Afhankelijk van de gebruikte tool (ISE, EDK of Vivado) kan de MIG Wizard een native FIFO-stijl of een AXI4-interface genereren om verbinding te maken met de gebruikerslogica. Deze workflow maakt de aanpassing mogelijk van verschillende DDR-parameters die zijn geoptimaliseerd voor de specifieke toepassing. Tabel 2 hieronder geeft een overzicht van de MIG Wizard-instellingen die zijn geoptimaliseerd voor de Arty.

| Instelling | Waarde |

| Geheugentype | DDR3 SDRAM |

| Maximale klokperiode | 3000 ps (datasnelheid van 667 Mbps) |

| Geheugendeel | MT41K128M16XX-15E |

| Geheugenspanning | 1,35 V |

| Gegevensbreedte | 16 |

| Gegevensmasker | Ingeschakeld |

| Aanbevolen klokperiode van de ingang | 6000 ps (166,667 MHz) |

| Impedantieregeling van de uitgangsdriver | RZQ/6 |

| Chipselect-pin van de controller | Ingeschakeld |

| Rtt (nominaal) – on-die termination | RZQ/6 |

| Interval Vref | Ingeschakeld |

| Interne afsluitimpedantie | 50 omhs |

Tabel 3. DDR3L-instellingen voor de Arty.

De MIG Wizard vereist dat de vaste pin-out van de geheugensignalen wordt ingevoerd en gevalideerd voordat de IP-core wordt gegenereerd. Voor uw gemak wordt een importeerbaar UCF-bestand geleverd op het Arty-resourcecentrum om dit proces te versnellen. Het is opgenomen in de download van de ontwerpbron "MIG Project". Deze download bevat ook een .prj-bestand dat in de wizard kan worden geïmporteerd om deze automatisch te configureren met de opties in tabel 2.

Raadpleeg de 7 Series FPGAs Memory Interface Solutions User Guide (ug586) voor meer informatie over de Xilinx MIG.

Quad-SPI Flash

FPGA-configuratiebestanden kunnen worden geschreven naar de Quad-SPI Flash (Micron-onderdeelnummer N25Q128A13ESF40) en door de mode-jumper in te stellen, zal de FPGA automatisch een configuratie van dit apparaat lezen bij het inschakelen. Een Artix-7 35T-configuratiebestand vereist 17.536.096 bits geheugen, waardoor ongeveer 87% van het flashapparaat (of ~14 MB) beschikbaar is voor gebruikersgegevens. Een veelvoorkomend gebruik voor dit extra geheugen is het opslaan van MicroBlaze-programma's die te groot zijn om in het on-board Block-geheugen te passen (meestal 128 KB). Deze programma's worden vervolgens geladen en uitgevoerd met behulp van een kleiner bootloader-programma dat in het blockgeheugen past. Het is mogelijk om deze bootloader automatisch te genereren, deze in een enkel bestand te rollen (een .mcs-bestand genoemd) dat ook de bitstream en uw aangepaste MicroBlaze-applicatie bevat, en dit bestand in SPI Flash te programmeren met behulp van Xilinx SDK en Vivado. Xilinx Answer Record 63605 legt uit hoe u dit moet doen.

De inhoud van het geheugen kan worden gemanipuleerd door bepaalde commando's op de SPI-bus te geven. De implementatie van dit protocol valt buiten het bestek van dit document. Alle signalen in de SPI-bus zijn I/O-pinnen voor algemeen gebruik na de FPGA-configuratie. Op andere kaarten is SCK een uitzondering omdat het een speciale pin blijft, zelfs na de configuratie. Op Arty wordt het SCK-signaal echter gerouteerd naar een extra pin voor algemeen gebruik die toegankelijk is na de configuratie (zie onderstaande afbeelding). Hierdoor is toegang tot deze pin mogelijk zonder de speciale FPGA-primitieve STARTUPE2 te hoeven instantiëren.

Xilinx's AXI Quad SPI-core kan worden gebruikt om de flash te lezen/schrijven in een MicroBlaze-ontwerp. Raadpleeg de productgids van Xilinx voor deze core voor meer informatie over het gebruik ervan, of het gegevensblad van Micron voor het flashapparaat om te leren hoe u een aangepaste controller kunt implementeren.

Ethernet PHY

Arty bevat een Texas Instruments 10/100 Ethernet PHY (TI-onderdeelnummer DP83848J) in combinatie met een RJ-45 Ethernet-aansluiting met geïntegreerde magneten en indicator-LED's. De TI PHY gebruikt de MII-interface en ondersteunt 10/100 Mb/s. Afbeelding 5 illustreert de pinverbindingen tussen de Artix-7 en de Ethernet PHY. Bij het inschakelen is de PHY ingesteld op de volgende standaardwaarden:

- MII-mode interface

- Auto-negotiation ingeschakeld, waarbij alle 10/100-modi worden geadverteerd

- PHY-adres=00001

- LED-modus 2

Twee LED's in de Ethernet-connector (J9) zijn aangesloten op de PHY om feedback te geven over de verbindingsstatus en data-activiteit. Zie het PHY-gegevensblad voor meer informatie. Houd er rekening mee dat het normaal is dat één LED brandt en één uit is, zelfs als de Ethernet PHY niet wordt gebruikt.

Op Vivado IPI gebaseerde ontwerpen hebben toegang tot de PHY met behulp van de AXI EthernetLite IP-core, de AXI 1G/2.5G Ethernet Subsystem IP-core of de Tri Mode Ethernet MAC IP-core. Er moet een klok van 25 MHz worden gegenereerd voor de X1-pin van de externe PHY, gelabeld als ETH_REF_CLK in het Arty-schema. Raadpleeg de Getting Started with MicroBlaze Serverstutorial van het Arty Resource Center om te leren hoe u de Ethernet PHY op de juiste manier gebruikt in een MicroBlaze-ontwerp op de Arty.

Raadpleeg het DP83848J-gegevensblad voor meer informatie over de Ethernet PHY.

Oscillatoren/klokken

De Arty-kaart bevat een enkele kristaloscillator van 100 MHz die is aangesloten op pin E3 (E3 is een MRCC-ingang op bank 35). De ingangsklok kan MMCM's of PLL's aansturen om klokken van verschillende frequenties te genereren en met bekende faserelaties die mogelijk nodig zijn in een ontwerp. Sommige regels beperken welke MMCM's en PLL's kunnen worden aangestuurd door de ingangsklok van 100 MHz. Raadpleeg de "7 Series FPGAs Clocking Resources User Guide" van Xilinx voor een volledige beschrijving van deze regels en de mogelijkheden van de Artix-7-klokbronnen.

Xilinx biedt de Clocking Wizard IP-core om gebruikers te helpen bij het genereren van de verschillende klokken die nodig zijn voor een specifiek ontwerp. Deze wizard zal de benodigde MMCM's en PLL's correct instantiëren op basis van de gewenste frequenties en faserelaties die door de gebruiker zijn gespecificeerd. De wizard voert vervolgens een eenvoudig te gebruiken wrapper-component uit rond deze klokbronnen die in het ontwerp van de gebruiker kan worden ingevoegd. De klokwizard is toegankelijk vanuit de Project Navigator- of Core Generator-tools.

USB-UART-brug (seriële poort)

De Arty bevat een FTDI FT2232HQ USB-UART-brug (aangesloten op connector J10) waarmee u pc-applicaties kunt gebruiken om met de kaart te communiceren met behulp van standaard Windows COM-poortopdrachten. Gratis USB-COM-poortdrivers, beschikbaar opwww.ftdichip.comonder het kopje "Virtual Com Port" of VCP, zetten USB-pakketten om in UART-/serieel poortgegevens. Seriële poortgegevens worden uitgewisseld met de FPGA met behulp van een seriële poort met twee draden (TXD/RXD). Nadat de drivers zijn geïnstalleerd, kunnen I/O-opdrachten vanaf de pc naar de COM-poort worden gestuurd om serieel dataverkeer op de A9- en D10 FPGA-pinnen te produceren.

Twee on-board status-LED's geven visuele feedback over verkeer dat door de poort stroomt: de zend-LED (LD10) en de ontvangst-LED (LD9). Signaalnamen die een richting impliceren, zijn vanuit het oogpunt van de DTE (Data Terminal Equipment), in dit geval de pc.

De FT2232HQ wordt ook gebruikt als controller voor de Digilent USB-JTAG-circuits, maar de USB-UART- en USB-JTAG-functies gedragen zich volledig onafhankelijk van elkaar. Programmeurs die geïnteresseerd zijn in het gebruik van de UART-functionaliteit van de FT2232 in hun ontwerp, hoeven zich geen zorgen te maken over de JTAG-circuits die de UART-gegevensoverdracht verstoren, en omgekeerd. De combinatie van deze twee functies in één apparaat maakt het mogelijk om de Arty te programmeren, ermee te communiceren via UART en van stroom te voorzien vanaf een computer die is aangesloten met een enkele micro-USB-kabel.

Het CK_RST-signaal (zie het Arty-schema) is ook via JP2 verbonden met het FT2232HQ-apparaat. Wanneer JP2 is kortgesloten, kan de FT2232HQ een MicroBlaze-reset activeren, waardoor het gedrag van Arduino- en chipKIT-kaarten wordt nagebootst wanneer sketches worden geladen. Merk op dat het CK_RST-signaal ook is verbonden met de rode RESET-knop en de RST-pin van J7 op de shieldconnector (deze verbindingen worden niet weergegeven in de onderstaande afbeelding).

De verbindingen tussen de FT2232HQ en de Artix-7 worden weergegeven in figuur 6.

Basis I/O

De Arty-kaart bevat vier driekleurige leds, 4 schakelaars, 4 drukknoppen, 4 individuele leds en een resetknop, zoals weergegeven in Afbeelding 16. De drukknoppen en schuifschakelaars zijn via serieweerstanden verbonden met de FPGA om schade door onbedoelde kortsluiting te voorkomen (een kortsluiting kan optreden als een FPGA-pin die is toegewezen aan een drukknop of schuifschakelaar per ongeluk is gedefinieerd als een uitgang). De vier drukknoppen zijn "kortstondige" schakelaars die normaal gesproken een lage uitvoer genereren als ze in ruststand staan, en een hoge uitvoer alleen wanneer ze worden ingedrukt. Schuifschakelaars genereren constante hoge of lage ingangen, afhankelijk van hun positie.

De rode resetknop met het label "RESET" genereert een hoge uitvoer in ruststand en een lage uitvoer wanneer deze wordt ingedrukt. De

RESET-knop is bedoeld om te worden gebruikt in MicroBlaze-ontwerpen om de processor te resetten, maar u kunt deze ook gebruiken als een algemene drukknop. Merk op dat deze ook is verbonden met de RST-pin op J7 van de shieldconnector en met het FT2232 UART-apparaat via JP2, hoewel deze verbindingen niet in de onderstaande afbeelding worden weergegeven.

De vier individuele energiezuinige leds zijn via weerstanden van 330 ohm met de anode verbonden met de FPGA, zodat ze worden ingeschakeld wanneer een logisch hoge spanning wordt toegepast op hun respectieve I/O-pin. Extra leds die niet toegankelijk zijn voor de gebruiker geven de status van de stroomvoorziening, de FPGA-programmering en de USB- en Ethernet-poort aan.

Driekleurige leds

De Arty-kaart bevat vier driekleurige leds. Elke driekleurige led heeft drie ingangssignalen die de kathoden van drie kleinere interne leds aansturen: één rode, één blauwe en één groene. Het hoog aansturen van het signaal dat overeenkomt met een van deze kleuren zal de interne led verlichten. De ingangssignalen worden door de FPGA via een transistor gestuurd, die de signalen omkeert. Om de driekleurige led te laten branden, moeten de bijbehorende signalen dus hoog worden aangestuurd. De driekleurige led zal een kleur uitzenden die afhankelijk is van de combinatie van interne leds die momenteel worden verlicht. Als bijvoorbeeld de rode en blauwe signalen hoog worden aangestuurd en groen laag wordt aangestuurd, zal de driekleurige led een paarse kleur uitzenden.

Opmerking: Digilent raadt ten zeerste aan om pulsbreedtemodulatie (PWM) te gebruiken bij het aansturen van de driekleurige leds. Het aansturen van een van de ingangen naar een stabiele logische '1' zal ertoe leiden dat de led op een oncomfortabel helder niveau wordt verlicht. U kunt dit voorkomen door ervoor te zorgen dat geen van de driekleursignalen wordt aangestuurd met meer dan een duty cycle van 50%. Het gebruik van PWM breidt ook het potentiële kleurenpalet van de driekleurige led aanzienlijk uit. Door de duty cycle van elke kleur afzonderlijk aan te passen tussen 50% en 0%, worden de verschillende kleuren met verschillende intensiteiten verlicht, waardoor vrijwel elke kleur kan worden weergegeven.

Pmod-connectoren

Pmod-connectoren zijn 2×6, haakse, 100-mil tussenliggende vrouwelijke connectoren die passen op standaard 2×6-pinheaders. Elke 12-pins Pmod-connector biedt twee 3,3V VCC-signalen (pinnen 6 en 12), twee aardingssignalen (pinnen 5 en 11) en acht logische signalen, zoals weergegeven in Fig. 16. De VCC- en aardingspinnen kunnen tot 1A stroom leveren, maar er moet op worden gelet dat de vermogensbudgetten van de ingebouwde regelaars of de externe voeding niet worden overschreden (deze worden beschreven in de sectie "Voedingen").

Digilent produceert een grote collectie Pmod-accessoirekaarten die kunnen worden aangesloten op de Pmod-uitbreidingsconnectoren om kant-en-klare functies toe te voegen, zoals A/D's, D/A's, motordrivers, sensoren en andere functies.

De Arty heeft vier Pmod-connectoren, waarvan sommige zich anders gedragen dan andere. Elke Pmod-connector valt in een van de twee categorieën: standaard of hoge snelheid. Tabel 9 specificeert in welke categorie elke Pmod valt en geeft ook de FPGA-pinnen weer waarmee ze zijn verbonden. In de volgende paragrafen worden de verschillende soorten Pmods beschreven.

| Pmod JA | Pmod JB | Pmod JC | Pmod JD | |

| Pmod-type | Standaard | Hoge snelheid | Hoge snelheid | Standaard |

| Pin 1 | G13 | E15 | U12 | D4 |

| Pin 2 | B11 | E16 | V12 | D3 |

| Pin 3 | A11 | D15 | V10 | F4 |

| Pin 4 | D12 | C15 | V11 | F3 |

| Pin 7 | D13 | J17 | U14 | E2 |

| Pin 8 | B18 | J18 | V14 | D2 |

| Pin 9 | A18 | K15 | T13 | H2 |

| Pin 10 | K16 | J15 | U13 | G2 |

Tabel 4. Pmod-connectorcategorieën.

Standaard Pmod

De standaard Pmod-connectoren zijn via serieweerstanden van 200 Ohm verbonden met de FPGA. De serieweerstanden voorkomen kortsluiting die kan optreden als de gebruiker per ongeluk een signaal aanstuurt dat als ingang moet worden gebruikt. Het nadeel van deze extra bescherming is dat deze weerstanden de maximale schakelsnelheid van de gegevenssignalen kunnen beperken. Als de gebruikte Pmod geen snelle toegang vereist, moet de standaard Pmod-connector worden gebruikt om schade aan de apparaten te voorkomen.

Pmod met hoge snelheid

De High-speed Pmods gebruiken de standaard Pmod-connector, maar hun gegevenssignalen zijn gerouteerd als impedantie-aangepaste differentiële paren voor maximale schakelsnelheden. Ze hebben pads voor het laden van weerstanden voor extra bescherming, maar de Arty wordt geleverd met deze geladen als 0-ohm shunts. Met de serieweerstanden ge-shunt, bieden deze Pmods geen bescherming tegen kortsluiting, maar maken ze veel snellere schakelsnelheden mogelijk. De signalen zijn gekoppeld aan de aangrenzende signalen in dezelfde rij: pinnen 1 en 2, pinnen 3 en 4, pinnen 7 en 8 en pinnen 9 en 10.

Traces zijn gerouteerd 100 ohm (+/- 10%) differentieel.

Deze connectoren mogen alleen worden gebruikt als snelle differentiële signalering vereist is of als de andere Pmods allemaal bezet zijn. Indien gebruikt als single-ended, kunnen gekoppelde paren aanzienlijke overspraak hebben. In toepassingen waarbij dit een probleem is, moet de standaard Pmod-connector worden gebruikt. Een andere optie is om een van de signalen te aarden (stuur het laag vanaf de FPGA) en het paar te gebruiken voor het single-ended signaal.

Aangezien de High-Speed Pmods 0-ohm shunts hebben in plaats van beschermingsweerstanden, moet de operator voorzorgsmaatregelen nemen om ervoor te zorgen dat ze geen kortsluiting veroorzaken.

Arduino/chipKIT Shield Connector

Arty kan worden aangesloten op standaard Arduino- en chipKIT-shields om uitgebreide functionaliteit toe te voegen. Er is speciale aandacht besteed aan het ontwerp van Arty om ervoor te zorgen dat het compatibel is met de meeste Arduino- en chipKIT-shields op de markt. De shieldconnector heeft 49 pinnen die zijn aangesloten op de FPGA voor algemeen digitaal I/O. Vanwege de flexibiliteit van FPGA's is het mogelijk om deze pinnen te gebruiken voor vrijwel alles, inclusief digitaal lezen/schrijven, SPI-verbindingen, UART-verbindingen, I2C-verbindingen en PWM. Zes van deze pinnen (gelabeld AN0-AN5) kunnen ook worden gebruikt als single-ended analoge ingangen met een ingangsbereik van 0V-3,3V, en nog eens zes (gelabeld AN6-11) kunnen worden gebruikt als differentiële analoge ingangen.

Opmerking: de Arty is niet compatibel met shields die digitale of analoge signalen van 5V uitvoeren. Het aansturen van pinnen op de Arty-shieldconnector boven 5V kan schade aan de FPGA veroorzaken.

De onderstaande afbeelding geeft een overzicht van de pinnen op de shieldconnector van de Arty.

| Pin Name | Shield Function | Arty Connection |

| IO0-IO13, IO26-IO41, A (IO42) | General purpose I/O pins | Zie het gedeelte met de titel "Shield Digital I/O" |

| SCL | I2C-klok | Zie het gedeelte met de titel "Shield Digital I/O" |

| SDA | I2C-gegevens | Zie het gedeelte met de titel "Shield Digital I/O" |

| SCLK | SPI-klok | Zie het gedeelte met de titel "Shield Digital I/O" |

| MOSI | SPI-gegevensuitvoer | Zie het gedeelte met de titel "Shield Digital I/O" |

| MISO | SPI-gegevensinvoer | Zie het gedeelte met de titel "Shield Digital I/O" |

| SS | SPI slave select | Zie het gedeelte met de titel "Shield Digital I/O" |

| A0-A5 | Single-ended analoge ingang | Zie het gedeelte met de titel "Shield Digital I/O" |

| A6-A11 | Differentiële analoge ingang | Zie het gedeelte met de titel "Shield Digital I/O" |

| V_P, V_N | Dedicated differentiële analoog | Zie het gedeelte met de titel "Shield Digital I/O" |

| XGND | input XADC analoog aarde | Aangesloten op het netwerk dat wordt gebruikt om de XADC-aarde-referentie op de FPGA aan te sturen (VREFN) |

| XVREF | XADC analoge spanning | Aangesloten op 1,25 V, 25 mA rail die wordt gebruikt om de XADC-spanningsreferentie op de FPGA aan te sturen (VREFP) |

| N/C | Niet aangesloten | Niet aangesloten |

| IOREF | Digital I/O-spanningsreferentie | Aangesloten op de Arty 3.3V-stroomrail (zie het gedeelte "Voedingen") |

| RST | Resetten naar shield | Aangesloten op de rode "RESET"-knop en een digitale I/O van de FPGA. Wanneer JP2 is kortgesloten, is deze ook aangesloten op het DTR-signaal van de FTDI USB-UART-brug. |

| 3V3 | 3.3V-stroomrail | Aangesloten op de Arty 3.3V-stroomrail (zie het gedeelte "Voedingen") |

| 5V0 | 5.0V-stroomrail | Aangesloten op de Arty 5.0V-stroomrail (zie het gedeelte "Voedingen") |

| GND, G | Aarde | Aangesloten op het aardvlak van Arty |

| VIN | Stroominvoer | Parallel geschakeld met de externe voedingsconnector (J12). Zie het gedeelte "Voedingen" voor informatie over het voeden van Arty via deze pin. |

Tabel 5. Shield-aansluittabel en functionele beschrijving.

Shield Digital I/O

De pinnen die rechtstreeks op de FPGA zijn aangesloten, kunnen worden gebruikt als algemene ingangen of uitgangen. Deze pinnen omvatten de I2C-, SPI- en algemene I/O-pinnen. Er zijn serieweerstanden van 200 Ohm tussen de FPGA en de digitale I/O-pinnen om bescherming te bieden tegen accidentele kortsluitingen. De absolute maximum- en aanbevolen bedrijfsspanningen voor deze pinnen worden in de onderstaande tabel weergegeven.

| Absolute Minimum Voltage | Recommended Minimum Operating Voltage | Recommended Maximum Operating Voltage | Absolute Maximum Voltage | |

| Powered | -0.4V | -0.2V | 3.4V | 3.75V |

| Unpowered | -0.4V | N/A | N/A | 0.55V |

Tabel 6. Absolute maximum- en aanbevolen bedrijfsspanningen.

Voor meer informatie over de elektrische kenmerken van de pinnen die zijn aangesloten op de FPGA, raadpleegt u deArtix-7datasheetfvan Xilinx.

Shield Analog I/O

De pinnen met het label A0-A11 en V_P/V_N worden gebruikt als analoge ingangen voor de XADC-module van de FPGA. De FPGA verwacht dat de ingangen variëren van 0-1 V. Op de pinnen met het label A0-A5 gebruiken we een extern circuit om de ingangsspanning te verlagen van 3,3V. Dit circuit wordt weergegeven in figuur 11.2.1. Dit circuit stelt de XADC-module in staat om nauwkeurig elke spanning tussen 0V en 3,3V (ten opzichte van de GND van de Arty) te meten die op een van deze pinnen wordt toegepast. Als u de pinnen met het label A0-A5 wilt gebruiken als digitale ingangen of uitgangen, zijn deze ook rechtstreeks aangesloten op de FPGA vóór het weerstandsdelingscircuit (ook weergegeven in figuur 11.2.1).

De pinnen met het label A6-A11 zijn rechtstreeks aangesloten op 3 paren analoog geschikte pinnen op de FPGA via een anti-aliasingfilter. Dit circuit wordt weergegeven in figuur 11.2.2. Deze paren pinnen kunnen worden gebruikt als differentiële analoge ingangen met een spanningsverschil tussen 0-1V. De even getallen zijn verbonden met de positieve pinnen van het paar en de oneven getallen zijn verbonden met de negatieve pinnen (dus A6 en A7 vormen een analoog ingangspaar waarbij A6 positief is en A7 negatief). Houd er rekening mee dat hoewel de pads voor de condensator aanwezig zijn, ze niet zijn geladen voor deze pinnen. Aangezien de analoog geschikte pinnen van de FPGA ook kunnen worden gebruikt als normale digitale FPGA-pinnen, is het ook mogelijk om deze pinnen te gebruiken voor Digital I/O.

De pinnen met het label V_P en V_N zijn aangesloten op de VP_0 en VN_0 dedicated analoge ingangen van de FPGA. Dit paar pinnen kan ook worden gebruikt als een differentiële analoge ingang met spanning tussen 0-1V, maar ze kunnen niet worden gebruikt als Digital I/O. De condensator in het circuit dat wordt weergegeven in figuur 11.2.2 voor dit paar pinnen is geladen op de Arty.

De XADC-kern in de Artix-7 is een tweekanaals 12-bits analoog-naar-digitaal converter die kan werken met 1 MSPS. Beide kanalen kunnen worden aangestuurd door een van de analoge ingangen die zijn aangesloten op de shieldpinnen. De XADC-kern wordt bediend en benaderd vanuit een gebruikersontwerp via de Dynamic Reconfiguration Port (DRP). De DRP biedt ook toegang tot spanningsmonitoren die aanwezig zijn op elk van de voedingsrails van de FPGA, en een temperatuursensor die zich in de FPGA bevindt. Raadpleeg voor meer informatie over het gebruik van de XADC-kern het Xilinx-document met de titel 7 Series FPGAs and Zynq-7000 All Programmable SoC XADC Dual 12-Bit 1 MSPS Analog-to-Digital Converter. Een demo die de XADC-kern gebruikt, is beschikbaar op het Arty-resourcecentrum.

Referenties

Download handleiding

Hier kunt u de volledige pdf-versie van de handleiding downloaden. Deze kan aanvullende veiligheidsinstructies, garantie-informatie, FCC-regels, enz. bevatten.

Download Digilent Arty Handleiding